# DS80C390 Dual CAN High-Speed Microprocessor

### www.maxim-ic.com

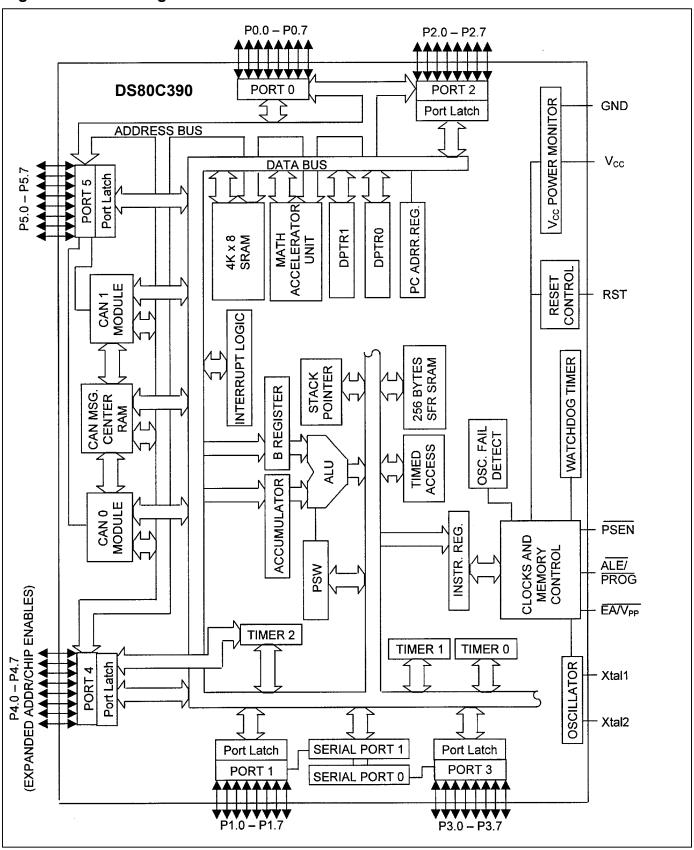

#### GENERAL DESCRIPTION

DS80C390 is a fast 8051-compatible microprocessor with dual CAN 2.0B controllers. The processor core executes instructions up to 3X faster than the original for the same crystal speed. The DS80C390 supports a maximum crystal speed of 40MHz, resulting in execution speeds 100MHz apparent of (approximately 2.5X). An optional internal frequency multiplier allows the microprocessor to operate at full speed with a reduced crystal frequency, reducing EMI. A hardware math accelerator further increases the speed of 32-bit and 16-bit multiply and divide operations as well as high-speed shift, normalization, and accumulate functions.

The High-Speed Microcontroller User's Guide and High-Speed Microcontroller User's Guide: DS80C390 Supplement must be used in conjunction with this data sheet. Download both at: www.maxim-ic.com/microcontrollers.

#### **APPLICATIONS**

Industrial Controls Factory Automation Medical Equipment Automotive Agricultural Equipment

Gaming Equipment

Heating, Ventilation, and

Air Conditioning

### **FEATURES**

- 80C52 Compatible

- High-Speed Architecture

- 4kB Internal SRAM Usable as Program/ Data/Stack Memory

- Enhanced Memory Architecture

- Two Full-Function CAN 2.0B Controllers

- Two Full-Duplex Hardware Serial Ports

- Programmable IrDA Clock

- High Integration Controller

- 16 Interrupt Sources with Six External

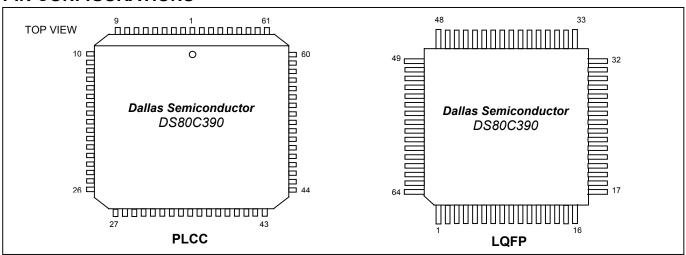

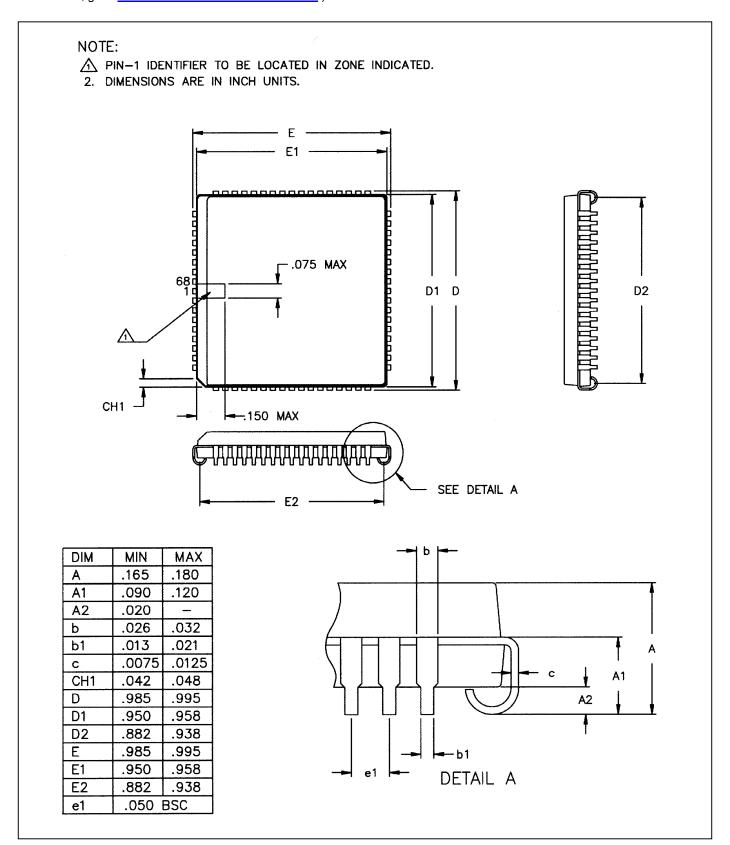

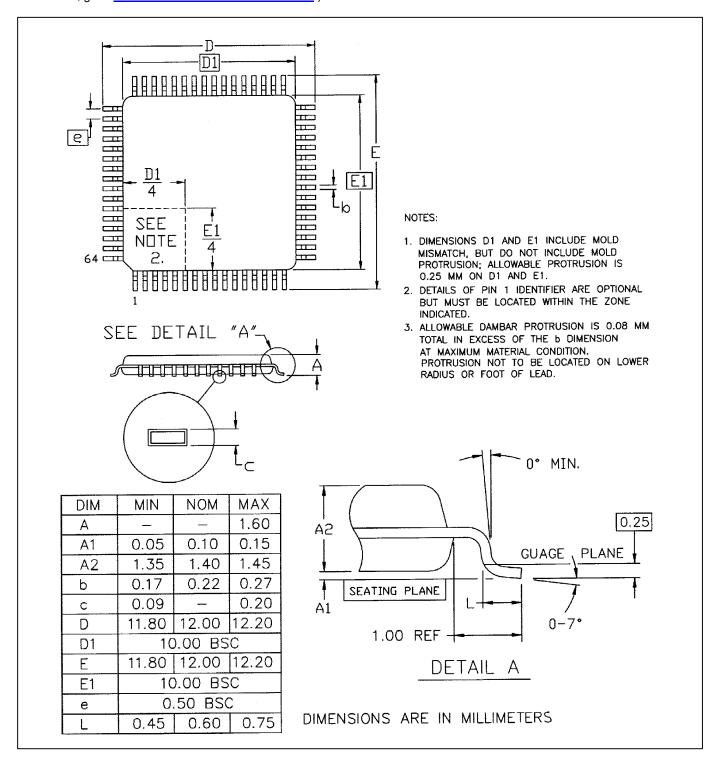

- Available in 64-Pin LQFP, 68-Pin PLCC

See page 29 for a complete list of features.

### ORDERING INFORMATION

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| DS80C390-QCR  | 0°C to +70°C   | 68 PLCC     |

| DS80C390-QCR+ | 0°C to +70°C   | 68 PLCC     |

| DS80C390-QNR  | -40°C to +85°C | 68 PLCC     |

| DS80C390-QNR+ | -40°C to +85°C | 68 PLCC     |

| DS80C390-FCR  | 0°C to +70°C   | 64 LQFP     |

| DS80C390-FCR+ | 0°C to +70°C   | 64 LQFP     |

| DS80C390-FNR  | -40°C to +85°C | 64 LQFP     |

| DS80C390-FNR+ | -40°C to +85°C | 64 LQFP     |

<sup>+</sup> Denotes a lead-free/RoHS-compliant device.

### PIN CONFIGURATIONS

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

1 of 54 REV: 110905

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground         | 0.3V to $(V_{CC} + 0.5V)$ |

|-----------------------------------------------------|---------------------------|

| Voltage Range on V <sub>CC</sub> Relative to Ground | 0.3V to +6.0V             |

| Operating Temperature Range                         | 40°C to +85°C             |

| Storage Temperature Range                           |                           |

| Soldering Temperature                               |                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

### **DC ELECTRICAL CHARACTERISTICS (Note 10)**

| PARAMETER                                                                                                                                                              | SYMBOL            | MIN                 | TYP  | MAX                  | UNITS    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|----------------------|----------|

| Supply Voltage                                                                                                                                                         | V <sub>CC</sub>   | $V_{RST}$           | 5.0  | 5.5                  | V        |

| Power-Fail Warning                                                                                                                                                     | $V_{PFW}$         | 4.10                | 4.38 | 4.60                 | V        |

| Minimum Operating Voltage                                                                                                                                              | V <sub>RST</sub>  | 3.85                | 4.13 | 4.35                 | V        |

| Supply Current, Active Mode (Note 1)                                                                                                                                   | I <sub>CC</sub>   |                     | 80   | 150                  | mA       |

| Supply Current, Idle Mode (Note 2)                                                                                                                                     | I <sub>IDLE</sub> |                     | 40   | 75                   | mA       |

| Supply Current, Stop Mode (Note 3)                                                                                                                                     | I <sub>STOP</sub> |                     | 1    | 120                  | μΑ       |

| Supply Current, Stop Mode, Bandgap Enabled (Note 3)                                                                                                                    | I <sub>SPBG</sub> |                     | 150  | 350                  | μΑ       |

| Input Low Level                                                                                                                                                        | $V_{IL}$          | -0.5                |      | +0.8                 | V        |

| Input High Level                                                                                                                                                       | $V_{IH}$          | 2.0                 |      | V <sub>CC</sub> +0.5 | V        |

| Input High Level for XTAL1, RST                                                                                                                                        | $V_{IH2}$         | $0.7 \times V_{CC}$ |      | $V_{CC}$ +0.5        | V        |

| Output Low Voltage for Port 1, 3, 4, 5 at I <sub>OL</sub> = 1.6mA                                                                                                      | V <sub>OL1</sub>  |                     |      | 0.45                 | V        |

| Output Low Voltage for Port 0, 1, 2, 4, 5, $\overline{RD}$ , $\overline{WR}$ , $\overline{RSTOL}$ , $\overline{PSEN}$ , and ALE at $I_{OL}$ = 3.2mA (Note 5)           | $V_{OL2}$         |                     |      | 0.45                 | V        |

| Output High Voltage for Port 1, 3, 4, 5 at I <sub>OH</sub> = -50μA (Note 4)                                                                                            | V <sub>OH1</sub>  | 2.4                 |      |                      | V        |

| Output High Voltage for Port 1, 3, 4, 5 at I <sub>OH</sub> = -1.5mA (Note 6)                                                                                           | V <sub>OH2</sub>  | 2.4                 |      |                      | V        |

| Output High Voltage for Port 0, 1, 2, 4, 5, $\overline{RD}$ , $\overline{WR}$ , $\overline{RSTOL}$ , $\overline{PSEN}$ , and ALE at I <sub>OH</sub> = -8mA (Note 5, 7) | V <sub>OH3</sub>  | 2.4                 |      |                      | <b>V</b> |

| Input Low Current for Port 1, 3, 4, 5 at 0.45V (Note 8)                                                                                                                | I₁∟               |                     |      | -55                  | μΑ       |

| Logic 1 to 0 Transition Current for Port 1, 3, 4, 5 (Note 9)                                                                                                           | I <sub>T1</sub>   |                     |      | -650                 | μA       |

| Input Leakage Current for Port 0 (Input Mode Only)                                                                                                                     | ΙL                | -300                |      | +300                 | μA       |

| RST Pulldown Resistance                                                                                                                                                | R <sub>RST</sub>  | 50                  |      | 170                  | kΩ       |

- Note 1: Active current measured with 40MHz clock source on XTAL1, V<sub>CC</sub> = RST = 5.5V, all other pins disconnected.

- Note 2: Idle mode current measured with 40MHz clock source on XTAL1,  $V_{CC}$ = 5.5V, RST =  $\overline{EA}$  =  $V_{SS}$ , all other pins disconnected.

- **Note 3:** Stop mode current measured with XTAL1 = RST =  $\overline{EA}$  = V<sub>SS</sub>, V<sub>CC</sub> = 5.5V, all other pins disconnected.

- **Note 4:** RST =  $V_{CC}$ . This condition mimics operation of pins in I/O mode.

- Note 5: Applies to port pins when they are used to address external memory or as CAN interface signals.

- Note 6: This measurement reflects the port during a 0-to-1 transition in I/O mode. During this period a one-shot circuit drives the ports hard for two clock cycles. If a port 4 or 5 pin is functioning in memory mode with pin state of 0 and the SFR bit contains a 1, changing the pin to an I/O mode (by writing to P4CNT) will not enable the 2-cycle strong pullup. During Stop or Idle mode the pins switch to I/O mode, and so port 2 and port 1 (in nonmultiplexed mode) will not exhibit the 2-cycle strong pullup when entering Stop or Idle mode.

- Note 7: Port 3 pins 3.6 and 3.7 have a stronger than normal pullup drive for one oscillator period following the transition of either the RD or WR from a 0-to-1 transition.

- Note 8: This is the current required from an external circuit to hold a logic low level on an I/O pin while the corresponding port latch bit is set to 1. This is only the current required to *hold* the low level; transitions from 1 to 0 on an I/O pin also have to overcome the transition current.

- **Note 9:** Ports 1(in I/O mode), 3, 4, and 5 source transition current when being pulled down externally. It reaches its maximum at approximately 2V.

- Note 10: Specifications to -40°C are guaranteed by design and not production tested.

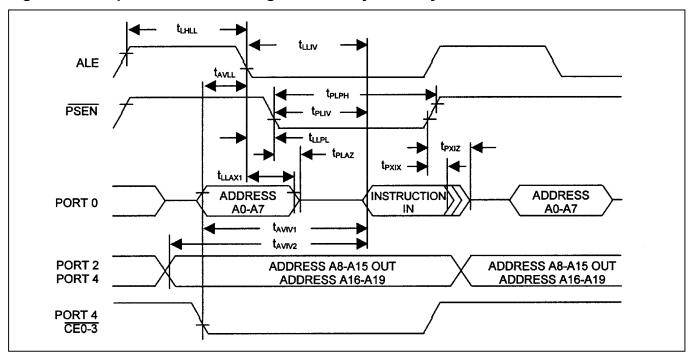

## AC ELECTRICAL CHARACTERISTICS—(MULTIPLEXED ADDRESS/DATA BUS) (Note 10, Note 11)

| PARAMETER                                                                           | SYMBOL                | CONDITIONS          | 40MHz |     | VARIABL                       | UNITS                       |         |

|-------------------------------------------------------------------------------------|-----------------------|---------------------|-------|-----|-------------------------------|-----------------------------|---------|

| FARAINETER                                                                          | STWIDOL               | CONDITIONS          | MIN   | MAX | MIN                           | MAX                         | UNITS   |

| Oscillator Frequency                                                                | 1 / t <sub>CLCL</sub> | External oscillator | 0     | 40  | 0                             | 40                          | MHz     |

| Oscillator Frequency                                                                | 1 / LCLCL             | External crystal    | 1     | 40  | 1                             | 40                          | IVII IZ |

| ALE Pulse Width                                                                     | t <sub>LHLL</sub>     |                     |       |     | 0.375 t <sub>MCS</sub><br>- 5 |                             | ns      |

| Port 0 Instruction Address or $\overline{\text{CE0}}\overline{-4}$ Valid to ALE Low | t <sub>AVLL</sub>     |                     |       |     | 0.125 t <sub>MCS</sub> - 5    |                             | ns      |

| Address Hold After ALE Low                                                          | t <sub>LLAX1</sub>    |                     |       |     | 0.125 t <sub>MCS</sub> - 5    |                             | ns      |

| ALE Low to Valid Instruction In                                                     | t <sub>LLIV</sub>     |                     |       |     |                               | 0.625 t <sub>MCS</sub> - 20 | ns      |

| ALE Low to PSEN Low                                                                 | t <sub>LLPL</sub>     |                     |       |     | 0.125 t <sub>MCS</sub> - 5    |                             | ns      |

| PSEN Pulse Width                                                                    | t <sub>PLPH</sub>     |                     |       |     | 0.5 t <sub>MCS</sub> - 8      |                             | ns      |

| PSEN Low to Valid Instruction In                                                    | t <sub>PLIV</sub>     |                     |       |     |                               | 0.5 t <sub>MCS</sub> - 20   | ns      |

| Input Instruction Hold After PSEN                                                   | t <sub>PXIX</sub>     |                     | 0     |     | 0                             |                             | ns      |

| Input Instruction Float After PSEN                                                  | t <sub>PXIZ</sub>     |                     |       |     |                               | $0.25~t_{\text{MCS}}$ - $5$ | ns      |

| Port 0 Address to Valid Instruction In                                              | t <sub>AVIV1</sub>    |                     |       |     |                               | 0.75 t <sub>MCS</sub> - 22  | ns      |

| Port 2, 4 Address to Valid Instruction In                                           | t <sub>AVIV2</sub>    |                     |       |     |                               | 0.875 t <sub>MCS</sub> - 30 | ns      |

| PSEN Low to Address Float                                                           | t <sub>PLAZ</sub>     |                     |       | 0   |                               | 0                           | ns      |

Note 11: All parameters apply to both commercial and industrial temperature operation unless otherwise noted. The value t<sub>MCS</sub> is a function of the machine cycle clock in terms of the processor's input clock frequency. These relationships are described in the *Stretch Value Timing* table. All signals characterized with load capacitance of 80pF except Port 0, ALE, PSEN, RD, and WR with 100pF. Interfacing to memory devices with float times (turn off times) over 25ns can cause bus contention. This does not damage the parts, but causes an increase in operating current. Specifications assume a 50% duty cycle for the oscillator. Port 2 and ALE timing changes in relation to duty cycle variation. Some AC timing characteristic drawings contain references to the CLK signal. This waveform is provided to assist in determining the relative occurrence of events and cannot be used to determine the timing of signals relative to the external clock. AC timing is characterized and guaranteed by design but is not production tested.

### **AC SYMBOLS**

The DS80C390 uses timing parameters and symbols similar to the original 8051 family. The following list of timing symbols is provided as an aid to understanding the timing diagrams.

| SYMBOL | FUNCTION                       |

|--------|--------------------------------|

| t      | Time                           |

| Α      | Address                        |

| С      | Clock                          |

| CE     | Chip Enable                    |

| D      | Input Data                     |

| Н      | Logic Level High               |

| L      | Logic Level Low                |

| I      | Instruction                    |

| Р      | PSEN                           |

| Q      | Output Data                    |

| R      | RD Signal                      |

| V      | Valid                          |

| W      | WR Signal                      |

| X      | No longer a valid logic level. |

| Z      | Tri-State                      |

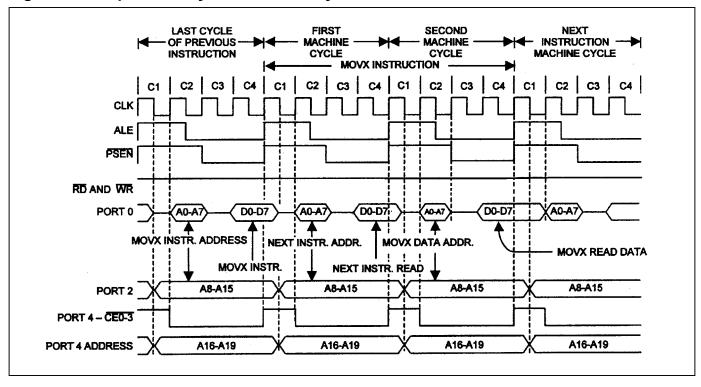

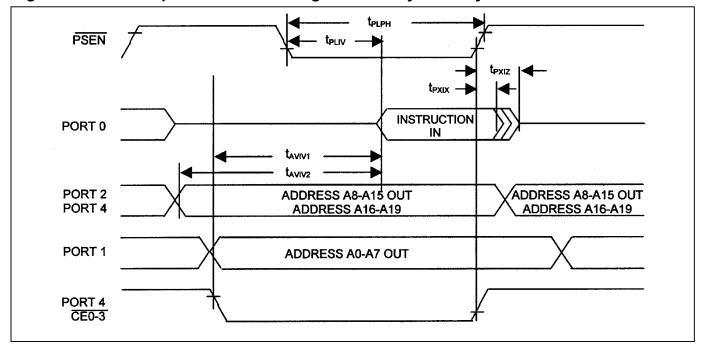

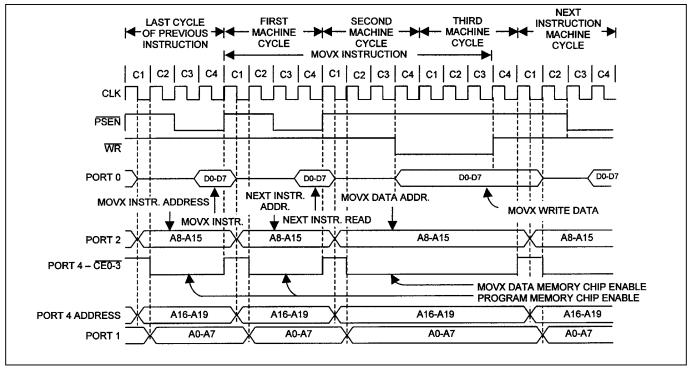

Figure 1. Multiplexed External Program Memory Read Cycle

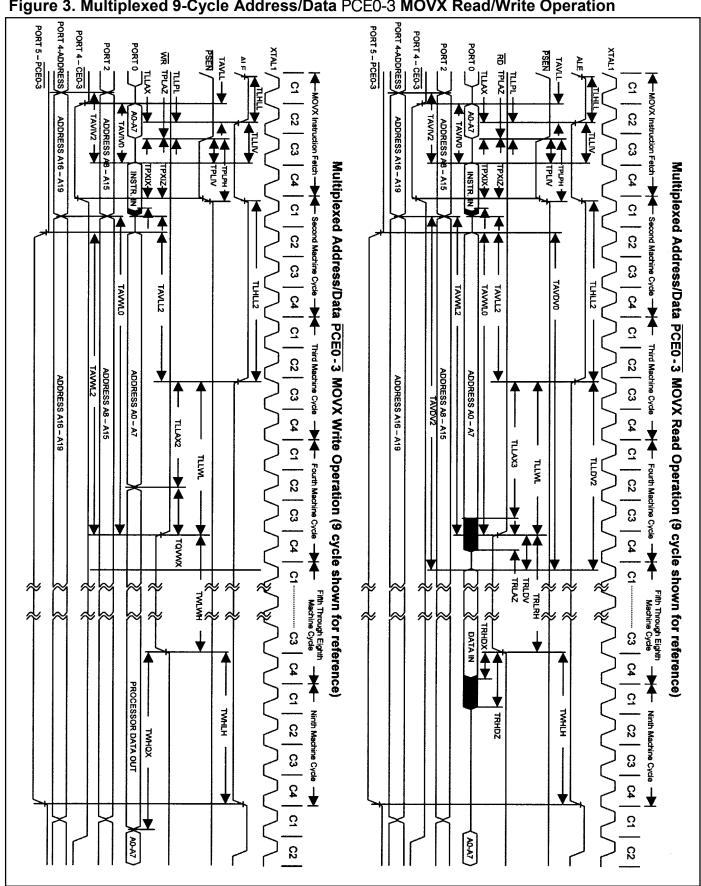

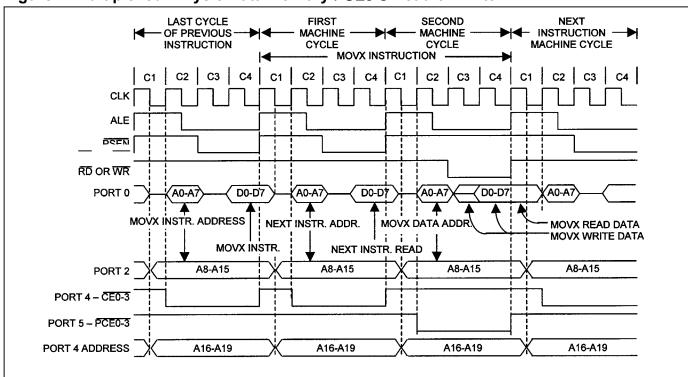

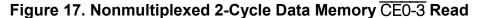

### MOVX CHARACTERISTICS (MULTIPLEXED ADDRESS/DATA BUS) (Note 12)

| PARAMETER                                                       | SYMBOL             | MIN                                     | MAX                                              | UNITS | STRETCH<br>VALUES       |

|-----------------------------------------------------------------|--------------------|-----------------------------------------|--------------------------------------------------|-------|-------------------------|

|                                                                 |                    | 0.075 / 5                               |                                                  |       | C <sub>ST</sub> (MD2:0) |

| MOVOVALE BULL MEN                                               | <b>│</b> . ⊢       | 0.375 t <sub>MCS</sub> - 5              |                                                  | ns    | $C_{ST} = 0$            |

| MOVX ALE Pulse Width                                            | t <sub>LHLL2</sub> | 0.5 t <sub>MCS</sub> - 5                |                                                  | ns    | 1 ≤ C <sub>ST</sub> ≤ 3 |

|                                                                 |                    | 1.5 t <sub>MCS</sub> - 10               |                                                  | ns    | 4 ≤ C <sub>ST</sub> ≤ 7 |

| Port 0 MOVX Address, $\overline{\text{CE0}}$ – $\overline{4}$ , |                    | 0.125 t <sub>MCS</sub> - 5              |                                                  | ns    | C <sub>ST</sub> = 0     |

| PCE0-4 Valid to ALE Low                                         | t <sub>AVLL2</sub> | 0.25t <sub>MCS</sub> - 5                |                                                  | ns    | 1≤ C <sub>ST</sub> ≤ 3  |

|                                                                 |                    | 1.25 t <sub>MCS</sub> - 10              |                                                  | ns    | $4 \le C_{ST} \le 7$    |

| Address Hold After MOVX                                         | t <sub>LLAX2</sub> | 0.25t <sub>MCS</sub> -5                 |                                                  | ns    | C <sub>ST</sub> = 0     |

| Read/Write                                                      | t <sub>LLAX3</sub> | 0.125 t <sub>MCS</sub> - 5              |                                                  | ns    | 1≤ C <sub>ST</sub> ≤ 3  |

|                                                                 | -LLANO             | 1.25 t <sub>MCS</sub> - 5               |                                                  | ns    | $4 \le C_{ST} \le 7$    |

| RD Pulse Width                                                  | t <sub>RLRH</sub>  | 0.5 t <sub>MCS</sub> - 6                |                                                  | ns    | $C_{ST} = 0$            |

| TIE T GIOC TVIGHT                                               | *KLKII             | C <sub>ST</sub> x t <sub>MCS</sub> - 10 |                                                  | ns    | $1 \le C_{ST} \le 7$    |

| WR Pulse Width                                                  | t <sub>WLWH</sub>  | 0.5 t <sub>MCS</sub> - 6                |                                                  | ns    | $C_{ST} = 0$            |

| VIII disc VIIdii                                                | *VVLVVIII          | C <sub>ST</sub> x t <sub>MCS</sub> - 10 |                                                  | ns    | $1 \le C_{ST} \le 7$    |

| RD Low to Valid Data In                                         | t <sub>RLDV</sub>  |                                         | 0.5 t <sub>MCS</sub> - 20                        | ns    | $C_{ST} = 0$            |

| TID LOW to Valid Bata III                                       | *RLDV              |                                         | C <sub>ST</sub> x t <sub>MCS</sub> - 25          | ns    | $1 \le C_{ST} \le 7$    |

| Data Hold After Read                                            | t <sub>RHDX</sub>  | 0                                       |                                                  | ns    |                         |

|                                                                 |                    |                                         | 0.25 t <sub>MCS</sub> - 5                        | ns    | $C_{ST} = 0$            |

| Data Float After Read                                           | t <sub>RHDZ</sub>  |                                         | 0.5t <sub>MCS</sub> - 5                          | ns    | $1 \le C_{ST} \le 3$    |

|                                                                 |                    |                                         | 1.5 t <sub>MCS</sub> - 5                         | ns    | $4 \le C_{ST} \le 7$    |

|                                                                 |                    |                                         | 0.625 t <sub>MCS</sub> - 20                      | ns    | C <sub>ST</sub> = 0     |

| ALE Low to Valid Data In                                        | t <sub>LLDV</sub>  |                                         | $(C_{ST} + 0.25) \times t_{MCS} - 20$            | ns    | 1 ≤ C <sub>ST</sub> ≤ 3 |

|                                                                 |                    |                                         | (C <sub>ST</sub> + 1.25) x t <sub>MCS</sub> - 20 | ns    | $4 \le C_{ST} \le 7$    |

|                                                                 |                    |                                         | 0.75 t <sub>MCS</sub> - 26                       | ns    | C <sub>ST</sub> = 0     |

| Port 0 Address, Port 4 CE, Port 5                               | t <sub>AVDV1</sub> |                                         | $(4C_{ST} + 0.5) \times t_{MCS} - 30$            | ns    | 1≤ C <sub>ST</sub> ≤ 3  |

| PCE to Valid Data In                                            |                    |                                         | $(4C_{ST} + 2.5) \times t_{MCS} - 30$            | ns    | $4 \le C_{ST} \le 7$    |

|                                                                 |                    |                                         | 0.75 t <sub>MCS</sub> - 30                       | ns    | C <sub>ST</sub> = 0     |

| Port 2, 4 Address to Valid Data In                              | t <sub>AVDV2</sub> |                                         | $(4C_{ST} + 0.5) \times t_{MCS} - 30$            | ns    | 1 ≤ C <sub>ST</sub> ≤ 3 |

| ,                                                               |                    |                                         | $(4C_{ST} + 2.5) \times t_{MCS} - 30$            | ns    | $4 \le C_{ST} \le 7$    |

|                                                                 |                    | 0.125 t <sub>MCS</sub> - 5              | 0.125 t <sub>MCS</sub> + 10                      | ns    | C <sub>ST</sub> =0      |

| ALE Low to RD or WR Low                                         | t <sub>LLWL</sub>  | 0.25t <sub>MCS</sub> - 5                | 0.25t <sub>MCS</sub> + 10                        | ns    | 1 ≤ C <sub>ST</sub> ≤ 3 |

| THE LOW TO THE ST THIN EST                                      | - LLVVL            | 1.25 t <sub>MCS</sub> - 5               | 1.25 t <sub>MCS</sub> + 10                       | ns    | $4 \le C_{ST} \le 7$    |

|                                                                 |                    | 0.25 t <sub>MCS</sub> - 11              | 1.23 twics - 10                                  | ns    | $C_{ST} = 0$            |

| Port 0 Address, Port 4 CE, Port 5                               | t <sub>AVWL1</sub> | 0.5t <sub>MCS</sub> - 11                |                                                  | ns    | $1 \le C_{ST} \le 3$    |

| PCE to RD or WR Low                                             | CAVVVLI            | 2.5 t <sub>MCS</sub> - 11               |                                                  | ns    | $4 \le C_{ST} \le 7$    |

|                                                                 | +                  | 0.375 t <sub>MCS</sub> - 11             |                                                  | ns    | $C_{ST} = 0$            |

| Port 2, 4 Address to or WR Low                                  | t <sub>AVWL2</sub> | 0.625t <sub>MCS</sub> - 11              |                                                  | ns    | $1 \le C_{ST} \le 3$    |

| 1 of 2, 4 Addiess to of Wit Low                                 | 4AVWL2             | 2.625 t <sub>MCS</sub> - 11             |                                                  | ns    | $4 \le C_{ST} \le 7$    |

| Data Valid to WR Transition                                     | t <sub>QVWX</sub>  | -8                                      |                                                  | ns    | 4 2 051 2 1             |

| - Late raile to TTT Transition                                  | -QVVV              |                                         |                                                  |       | 0 0                     |

| Data Hold After WR High                                         | <u> </u>           | 0.25 t <sub>MCS</sub> - 8               |                                                  | ns    | $C_{ST} = 0$            |

|                                                                 | t <sub>WHQX</sub>  | 0.5t <sub>MCS</sub> - 10                |                                                  | ns    | 1 ≤ C <sub>ST</sub> ≤ 3 |

|                                                                 |                    | 1.5 t <sub>MCS</sub> - 10               |                                                  | ns    | $4 \le C_{ST} \le 7$    |

| RD Low to Address Float                                         | t <sub>RLAZ</sub>  |                                         | See Note 12                                      |       |                         |

| RD or WR High to ALE, Port 4 CE                                 |                    | -5                                      | +10                                              | ns    | $C_{ST} = 0$            |

| or Port 5 PCE High                                              | t <sub>WHLH</sub>  | $0.25 t_{MCS} - 7$                      | $0.25 t_{MCS} + 5$                               | ns    | $1 \leq C_{ST} \leq 3$  |

|                                                                 |                    | 1.25 t <sub>MCS</sub> - 7               | 1.25 t <sub>MCS</sub> +10                        | ns    | $4 \le C_{ST} \le 7$    |

Note 12: All parameters apply to both commercial and industrial temperature operation.  $C_{ST}$  is the stretch cycle value determined by the MD2:0 bits.  $t_{MCS}$  is a time period shown in the  $t_{MCS}$  Time Periods table. All signals characterized with load capacitance of 80pF except Port 0, ALE,  $\overline{PSEN}$ ,  $\overline{RD}$ , and  $\overline{WR}$  with 100pF. Interfacing to memory devices with float times over 25ns can cause bus contention and an increase in operating current. Specifications assume a 50% duty cycle for the oscillator; port 2 and ALE timing changes in relation to duty cycle variation. Some AC timing characteristic drawings show the CLK signal, provided to determine the relative occurrence of events and not the timing of signals relative to the external clock. During the external addressing mode, weak latches maintain the previously driven value from the processor on Port 0 until Port 0 is overdriven by external memory; and on Port 1, 2 and 4 for one XTAL1 cycle prior to change in output address from Port 1, 2, and 4.

PORT 4-ADDRESS ORT 4-ADDRESS A-MOVX Instruction Felch - A-Second Machine Cycle - A-Third Machine Cycle - A-Fourth Machine Cyc 9 ADDRESS A16 - A19 ADDRESS A16 - A19 TPLN T Multiplexed Address/Data CE0-3 MOVX Write Operation (9 cycle shown for reference) Multiplexed Address/Data CE0-3 MOVX Read Operation (9 cycle shown for reference) TPXIX-TPXIX-▼  $\Omega$ INSTR. IN -A15  $\Omega$ ႙ ႙ TAVWL2 Ω  $\mathfrak{Q}$  $\Omega$  $\overline{\varsigma}$ ន ADDRESS A8 - A15 ADDRESS A8 - A15 ADDRESS A0 - A7 ADDRESS A16 - A19 ADDRESS A16 - A19 င္ယ င္ယ  $\mathfrak{Q}$  $\mathfrak{Q}$ TLLAX2 TLLAX3  $\overline{\sigma}$ 2 ន ន ဌ 2 TQWX δ Fifth Through Eighth Machine Cycle ដ ŝ DATA IN  $\mathfrak{Q}$ Ω PROCESSOR DATA OUT  $\overline{\sigma}$ Ω HHWT THAT ន ន င္ယ Ω  $\overline{\mathbf{c}}$  $\overline{\sigma}$ A0-A7 ខ្ល

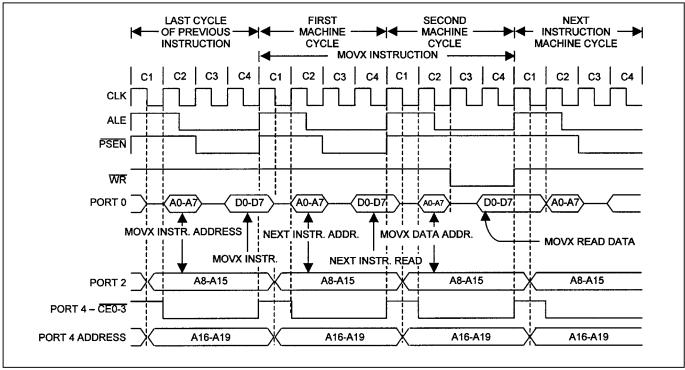

Figure 2. Multiplexed 9-Cycle Address/Data CE0-3 MOVX Read/Write Operation

Figure 3. Multiplexed 9-Cycle Address/Data PCE0-3 MOVX Read/Write Operation

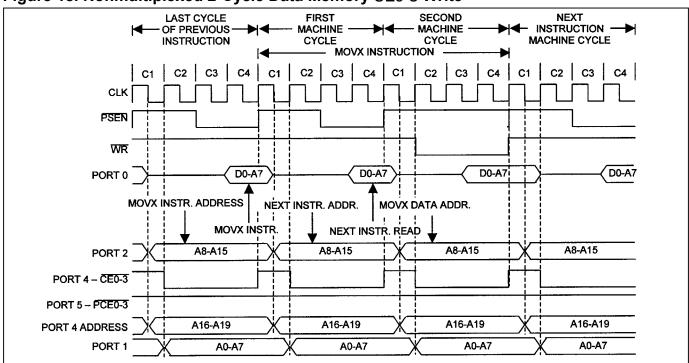

Figure 4. Multiplexed 2-Cycle Data Memory PCE0-3 Read or Write

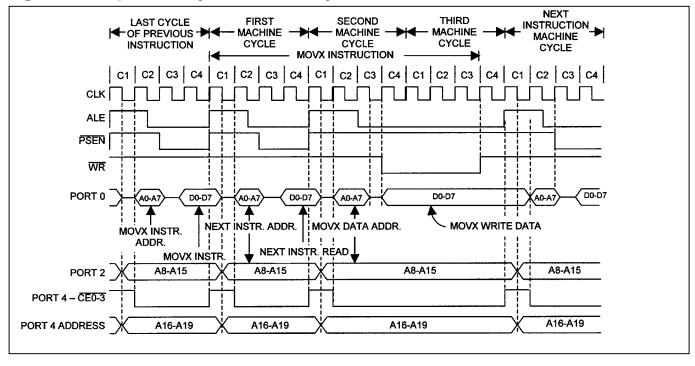

Figure 6. Multiplexed 2-Cycle Data Memory CEO-3 Write

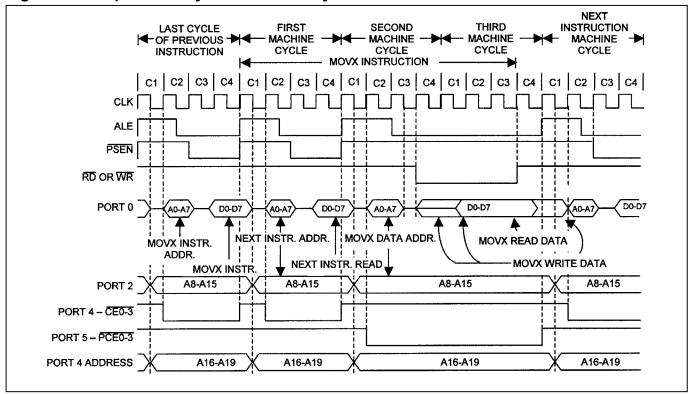

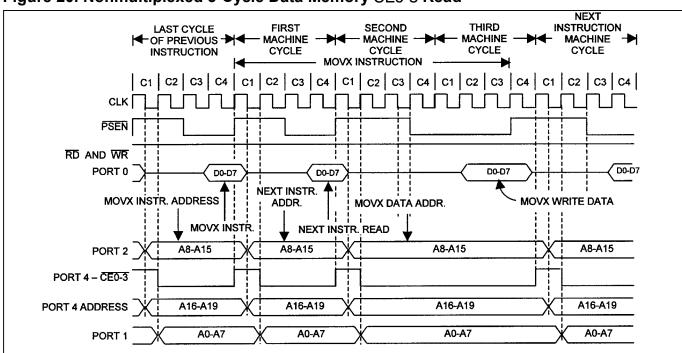

Figure 7. Multiplexed 3-Cycle Data Memory PCE0-3 Read or Write

Figure 8. Multiplexed 3-Cycle Data Memory CEO-3 Read

Figure 9. Multiplexed 3-Cycle Data Memory CEO-3 Write

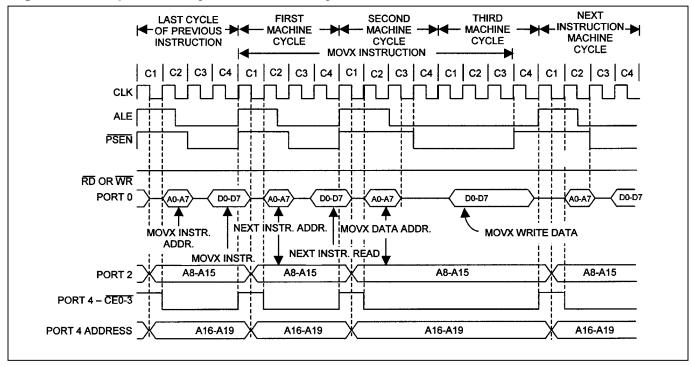

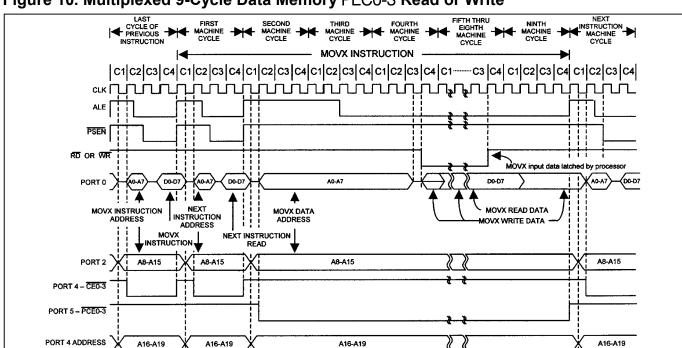

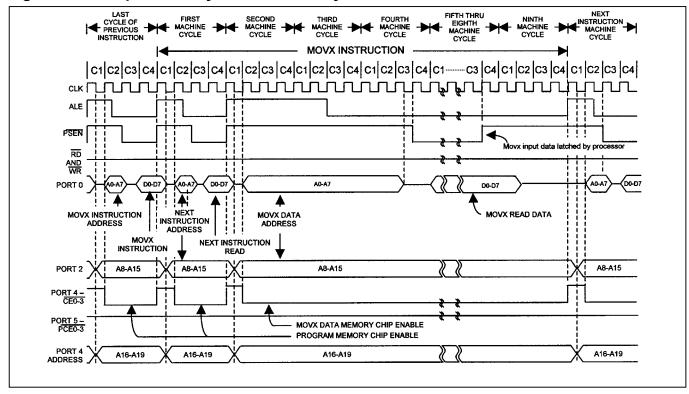

Figure 10. Multiplexed 9-Cycle Data Memory PEC0-3 Read or Write

A16-A19

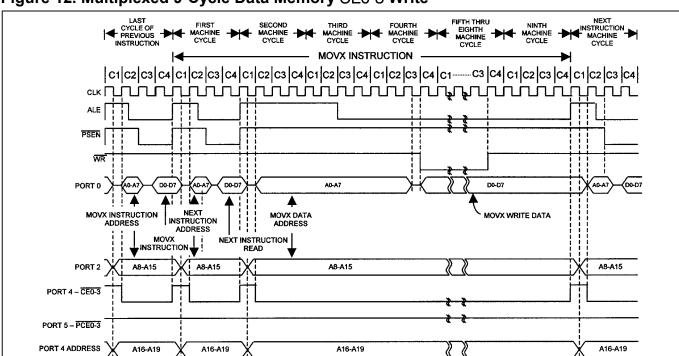

Figure 12. Multiplexed 9-Cycle Data Memory CEO-3 Write

A16-A19

A16-A19

## ELECTRICAL CHARACTERISTICS—(NONMULTIPLEXED ADDRESS/DATA BUS) (Note 13)

| PARAMETER                                         | SYMBOL                | CONDITIONS          | 401 | ИHz | VARIA                    | UNITS                        |         |  |

|---------------------------------------------------|-----------------------|---------------------|-----|-----|--------------------------|------------------------------|---------|--|

| TANAMETER                                         | STRIBOL               | CONDITIONS          | MIN | MAX | MIN                      | MAX                          | 700     |  |

| Oscillator Frequency                              | 1 / t <sub>CLCL</sub> | External oscillator | 0   | 40  | 0                        | 40                           | MHz     |  |

| Oscillator i requericy                            | 1 / tCLCL             | External crystal    | 1   | 40  | 1                        | 40                           | IVII IZ |  |

| PSEN Pulse Width                                  | $t_{PLPH}$            |                     |     |     | 0.5 t <sub>MCS</sub> - 8 |                              | ns      |  |

| PSEN Low to Valid Instruction In                  | t <sub>PLIV</sub>     |                     |     |     |                          | $0.5\ t_{\text{MCS}}$ - $20$ | ns      |  |

| Input Instruction Hold After PSEN                 | t <sub>PXIX</sub>     |                     | 0   |     | 0                        |                              | ns      |  |

| Input Instruction Float After PSEN                | t <sub>PXIZ</sub>     |                     |     |     |                          | See MOVX<br>Characteristics  | ns      |  |

| Port 1 Address, Port 4 CE to Valid Instruction In | t <sub>AVIV1</sub>    |                     |     |     |                          | 0.75 t <sub>MCS</sub> - 22   | ns      |  |

| Port 2, 4 Address to Valid Instruction In         | t <sub>AVIV2</sub>    |                     |     |     |                          | 0.875 t <sub>MCS</sub> - 30  | ns      |  |

Note 13: All parameters apply to both commercial and industrial temperature operation unless otherwise noted. The value t<sub>MCS</sub> is a function of the machine cycle clock in terms of the processor's input clock frequency. These relationships are described in the *Stretch Value Timing* table. All signals characterized with load capacitance of 80pF except Port 0, ALE, PSEN, RD, and WR with 100pF. Interfacing to memory devices with float times (turn off times) over 25ns can cause bus contention. This does not damage the parts, but causes an increase in operating current. Specifications assume a 50% duty cycle for the oscillator. Port 2 and ALE timing changes in relation to duty cycle variation. Some AC timing characteristic drawings contain references to the CLK signal. This waveform is provided to assist in determining the relative occurrence of events and cannot be used to determine the timing of signals relative to the external clock

Figure 13. Nonmultiplexed External Program Memory Read Cycle

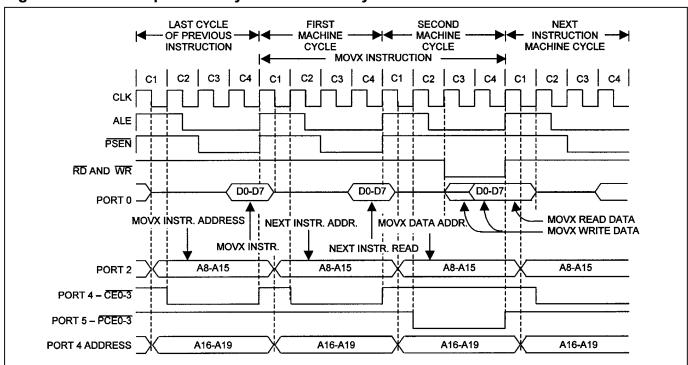

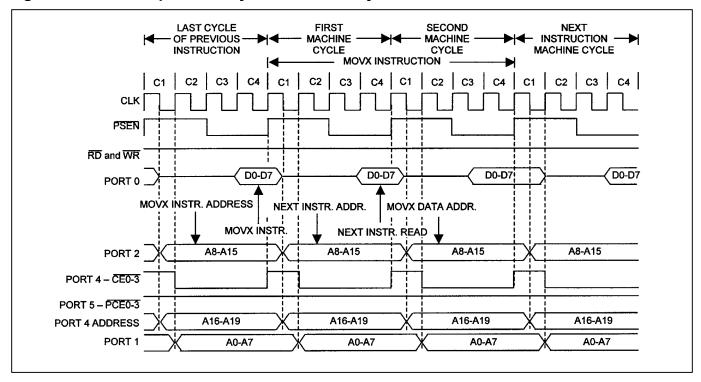

### MOVX CHARACTERISTICS (NONMULTIPLEXED ADDRESS/DATA BUS)

| PARAMETER                                          | SYMBOL             | MIN                                    | MAX                                     | UNITS | STRETCH<br>VALUES<br>C <sub>ST</sub> (MD2:0) |

|----------------------------------------------------|--------------------|----------------------------------------|-----------------------------------------|-------|----------------------------------------------|

| RD Pulse Width                                     | t <sub>RLRH</sub>  | 0.5 t <sub>MCS</sub> - 6               |                                         | ns    | $C_{ST} = 0$                                 |

| 113 1 4.00 11.44.                                  | TALINIT            | C <sub>ST</sub> x t <sub>MCS</sub> - 6 |                                         |       | $1 \le C_{ST} \le 7$                         |

| WR Pulse Width                                     | t <sub>WLWH</sub>  | 0.5 t <sub>MCS</sub> - 6               |                                         | ns    | C <sub>ST</sub> = 0                          |

|                                                    |                    | C <sub>ST</sub> x t <sub>MCS</sub> - 6 | 0.51                                    |       | 1 ≤ C <sub>ST</sub> ≤ 7                      |

| RD Low to Valid Data In                            | t <sub>RLDV</sub>  |                                        | 0.5 t <sub>MCS</sub> - 20               | ns    | $C_{ST} = 0$                                 |

| D                                                  | ,                  | •                                      | C <sub>ST</sub> x t <sub>MCS</sub> - 25 |       | $1 \le C_{ST} \le 7$                         |

| Data Hold After Read                               | t <sub>RHDX</sub>  | 0                                      |                                         | ns    |                                              |

|                                                    |                    |                                        | 0.125 t <sub>MCS</sub> - 5              |       | $C_{ST} = 0$                                 |

| Data Float After Read                              | t <sub>RHDZ</sub>  |                                        | 0.375t <sub>MCS</sub> - 5               | ns    | $1 \leq C_{ST} \leq 3$                       |

|                                                    |                    |                                        | 1.375 t <sub>MCS</sub> - 5              |       | $4 \leq C_{ST} \leq 7$                       |

| Port 1 Address, Port 4 CE, Port 5                  |                    |                                        | 0.75 t <sub>MCS</sub> - 26              |       | $C_{ST} = 0$                                 |

| PCE to Valid Data In                               | t <sub>AVDV1</sub> |                                        | $(4C_{ST} + 0.5) \times t_{MCS} - 30$   | ns    | $1 \leq C_{ST} \leq 3$                       |

| 1 of to valid bata in                              |                    |                                        | $(4C_{ST} + 2.5) \times t_{MCS} - 30$   |       | $4 \le C_{ST} \le 7$                         |

|                                                    | t <sub>AVDV2</sub> |                                        | 0.75 t <sub>MCS</sub> - 30              |       | $C_{ST} = 0$                                 |

| Port 2, 4 Address to Valid Data In                 |                    |                                        | $(4C_{ST} + 0.625) \times t_{MCS} - 30$ | ns    | $1 \leq C_{ST} \leq 3$                       |

|                                                    |                    |                                        | $(4C_{ST} + 2.625) \times t_{MCS} - 30$ |       | $4 \leq C_{ST} \leq 7$                       |

| Port 0 Address, Port 4 CE, Port 5                  |                    | 0.25 t <sub>MCS</sub> - 11             |                                         |       | C <sub>ST</sub> = 0                          |

| PCE to RD or WR Low                                | t <sub>AVWL1</sub> | 0.5 t <sub>MCS</sub> - 11              |                                         | ns    | $1 \leq C_{ST} \leq 3$                       |

|                                                    |                    | 2.5 t <sub>MCS</sub> - 11              |                                         |       | $4 \leq C_{ST} \leq 7$                       |

|                                                    |                    | 0.375 t <sub>MCS</sub> - 11            |                                         |       | $C_{ST} = 0$                                 |

| Port 2, 4 Address to RD or WR Low                  | t <sub>AVWL2</sub> | 0.625t <sub>MCS</sub> - 11             |                                         | ns    | $1 \le C_{ST} \le 3$                         |

|                                                    |                    | 2.625 t <sub>MCS</sub> - 11            |                                         |       | $4 \leq C_{ST} \leq 7$                       |

| Data Valid to $\overline{WR}$ Transition           | $t_{QVWX}$         | -8                                     |                                         | ns    |                                              |

| Data Hold After WR High                            |                    | 0.25 t <sub>MCS</sub> - 8              |                                         |       | C <sub>ST</sub> = 0                          |

|                                                    | $t_{WHQX}$         | 0.5t <sub>MCS</sub> - 10               |                                         | ns    | $1 \leq C_{ST} \leq 3$                       |

| -                                                  |                    | 1.5 t <sub>MCS</sub> - 10              |                                         |       | $4 \leq C_{ST} \leq 7$                       |

|                                                    |                    | -5                                     | 10                                      |       | $C_{ST} = 0$                                 |

| RD or WR High to ALE, Port 4 CE or Port 5 PCE High | twhlh              | 0.25 t <sub>MCS</sub> - 7              | 0.25 t <sub>MCS</sub> + 10              | ns    | $1 \leq C_{ST} \leq 3$                       |

| TOIL OT CETTIGHT                                   |                    | 1.25 t <sub>MCS</sub> - 7              | 1.25 t <sub>MCS</sub> + 10              |       | $4 \leq C_{ST} \leq 7$                       |

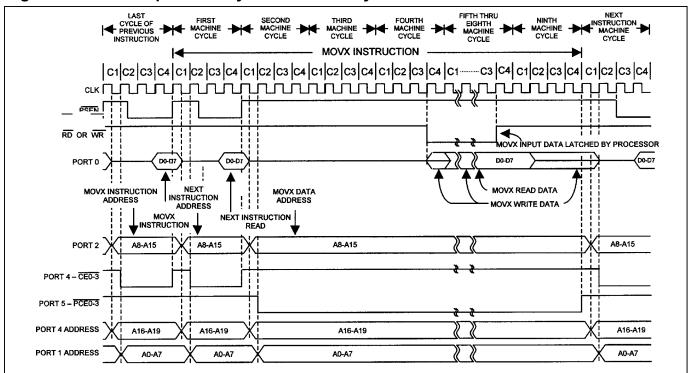

PORT 4-ADDRESS PORT 4 - CEO-3 PORT 0 MOVX Instruction Fetch — ADDRESS A0 - A7 ADDRESS A0 - A7 ADDRESS A8 - A15 င္ယ TPLIV πρχιz **→** TPXIZ ♥ TPLIV Non-Multiplexed Address/Data CE0-3 MOVX Write Operation (9 cycle shown for reference) Non-Multiplexed Address/Data CE0-3 MOVX Read Operation (9 cycle shown for reference) 2  $\Omega$ 2 2 TAVDV2 TAWWL2 TAWML2 ន្ត TPHRL TPHRL ADDRESS A8 -- A15 ADDRESS A0 - A7 2  $\mathbf{c}$ TQVWX ន ន င္ယ Ω 2 2 င္သ င္ယ 2 2 PROCESSOR DATA OUT ន ន 2 Ω

Figure 14. Nonmultiplexed 9-Cycle Address/Data CEO-3 MOVX Read/Write Operation

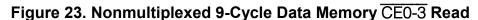

PORT 4-ADDRESS PORT 4-ADDRESS PORT 5 - PCEO-3 낑 ន ADDRESS A16 - A19 ADDRESS A0 - A7 ADDRESS A16 - A19 င္ယ Non-Multiplexed Address/Data PCE0-3 MOVX Read Operation (9 cycle shown for reference) Non-Multiplexed Address/Data PCE0-3 MOVX Write Operation (9 cycle shown for reference) TPLIV ★ XIX4⊥

▼ ZIX4⊥ TPLV ΠΡΧΙΖ ❤ ΠΡΧΙΧ ❤ 2 2 Ω  $\overline{\Omega}$ ន ន TPHAV TPHAV ឩ င္ယ 2  $\mathfrak{Q}$ Third Machine Cycle - Fourth Machine Cycle - $\mathfrak{Q}$ ន ន TPHWL TPHRL ADDRESS A8 - A15 ADDRESS A16 -- A19 ADDRESS A8 - A15 ADDRESS A0 - A7 ADDRESS A0 - A7 င္သ င္ယ 2 2  $\overline{\varsigma}$  $\mathfrak{Q}$ TOWX ន ន င္ယ င္ယ Ω  $\mathfrak{Q}$ 2 Fifth Through Eighth Machine Cycle င္ယ င္သ Ω PROCESSOR DATA OUT 2 Ninth Machine Cycle 2 TWHCEH ន XOHWL ន င္ယ  $\mathfrak{Q}$  $\Omega$ 2 A0-A7 ន ႙

Figure 15. Nonmultiplexed 9-Cycle Address/Data PCE0-3 MOVX Read/Write Operation

Figure 16. Nonmultiplexed 2-Cycle Data Memory PCE0 - 3 Read or Write

Figure 18. Nonmultiplexed 2-Cycle Data Memory CE0-3 Write

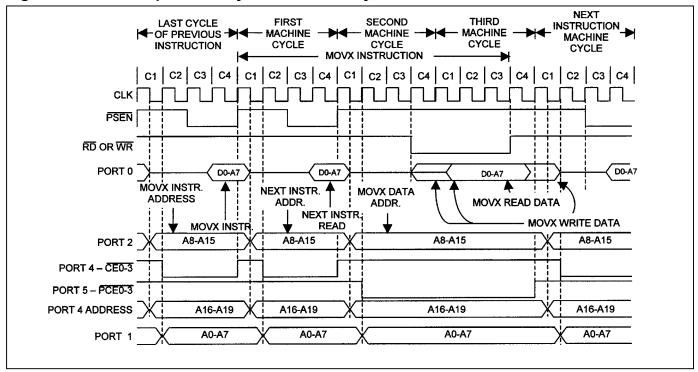

Figure 20. Nonmultiplexed 3-Cycle Data Memory CE0-3 Read

Figure 22. Nonmultiplexed 9-Cycle Data Memory PCE0-3 Read or Write

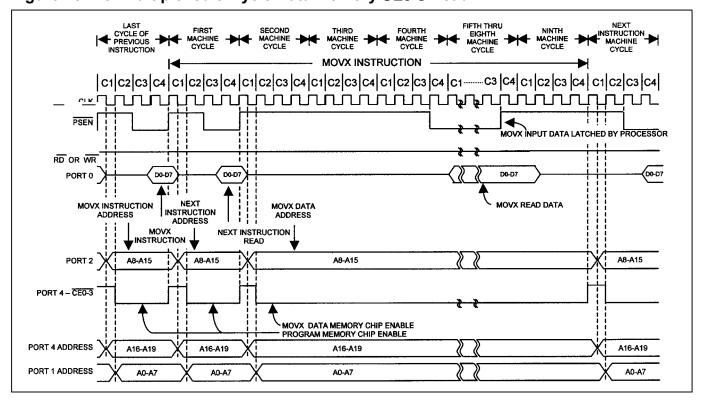

LAST

CYCLE OF

PREVIOUS

INSTRUCTION FIFTH THRU EIGHTH MACHINE CYCLE NEXT

INSTRUCTION

MACHINE

CYCLE FIRST MACHINE -SECOND MACHINE CYCLE THIRD MACHINE CYCLE FOURTH MACHINE CYCLE NINTH MACHINE CYCLE MOVX INSTRUCTION | C1|C2|C3|C4| C1|C2|C3|C4| C1|C2|C3|C4| C1|C2|C3|C4| C1|C2|C3|C4| C1|C2|C3|C4| C1------C3|C4| C1|C2|C3|C4| C1|C2|C3|C4| PSEN WR D0-D7 D0-D7 D0-D7 PORT 0 D0-D7 NEXT INSTRUCTION ADDRESS MOVX WRITE DATA MOVX INSTRUCTION MOVX DATA **ADDRESS** MOVX INSTRUCTION NEXT INSTRUCTION READ A8-A15 A8-A15 PORT 2 A8-A15 A8-A15 PORT 4 - CEO-3 MOVX DATA MEMORY CHIP ENABLE PROGRAM MEMORY CHIP ENABLE PORT 4 ADDRESS A16-A19 A16-A19 A16-A19 A16-A19 PORT 1 ADDRESS A0-A7

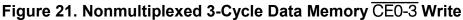

Figure 24. Nonmultiplexed 9-Cycle Data Memory CE0-3 Write

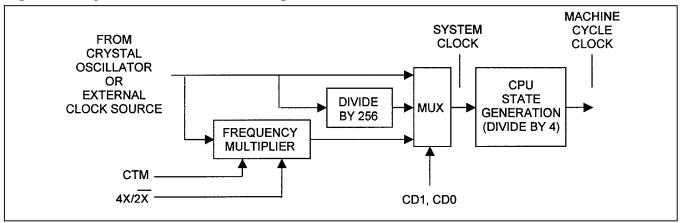

### **t<sub>MCS</sub> TIME PERIODS**

| SYSTE | M CLOCK SE | _   |                        |

|-------|------------|-----|------------------------|

| 4X/2X | CD1        | CD0 | t <sub>MCS</sub>       |

| 1     | 0          | 0   | 1 t <sub>CLCL</sub>    |

| 0     | 0          | 0   | 2 t <sub>CLCL</sub>    |

| X     | 1          | 0   | 4 t <sub>CLCL</sub>    |

| X     | 1          | 1   | 1024 t <sub>CLCL</sub> |

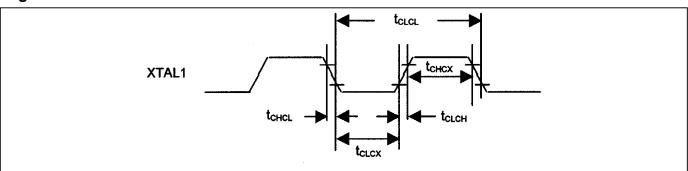

### **EXTERNAL CLOCK CHARACTERISTICS**

| PARAMETER       | SYMBOL            | MIN | MAX | UNITS |

|-----------------|-------------------|-----|-----|-------|

| Clock High Time | t <sub>CHCX</sub> | 8   |     | ns    |

| Clock Low Time  | t <sub>CLCX</sub> | 8   |     | ns    |

| Clock Rise Time | t <sub>CLCH</sub> |     | 4   | ns    |

| Clock Fall Time | t <sub>CHCL</sub> |     | 4   | ns    |

Figure 25. External Clock Drive

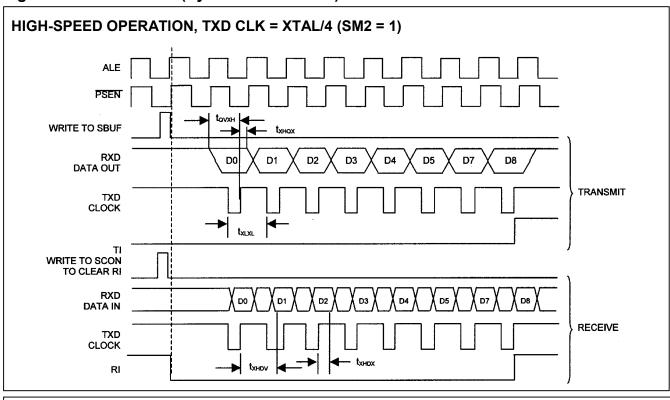

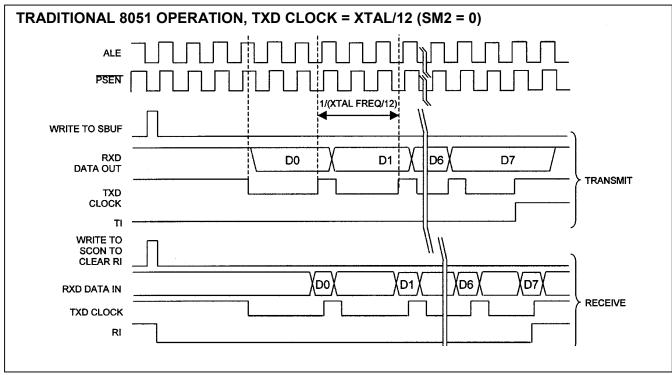

### **SERIAL PORT MODE 0 TIMING CHARACTERISTICS**

| PARAMETER                             | SYMBOL             | CONDITIONS                                           | TYP                  | UNITS |

|---------------------------------------|--------------------|------------------------------------------------------|----------------------|-------|

| Serial Port Clock Cycle Time          | t <sub>xi xi</sub> | SM2 = 0:2 clocks per cycle                           | 12 t <sub>clcl</sub> | ns    |

| Senai Fort Clock Cycle Time           | <b>L</b> XLXL      | SM2 = 1:4 clocks per cycle                           | 4 t <sub>CLCL</sub>  | 115   |

| Output Data Setup to Clock Rising     | t <sub>ovxH</sub>  | SM2 = 0:12 clocks per cycle                          | 10 t <sub>CLCL</sub> | ns    |

| Output Data Octup to Glock Maing      | <b>L</b> QVXH      | SM2 = 1:4 clocks per cycle                           | 3 t <sub>CLCL</sub>  | 113   |

| Output Data Hold from Clock Rising    | $t_{x \mapsto ox}$ | M2 = 0:12 clocks per cycle                           | 2 t <sub>CLCL</sub>  | ns    |

| Output Data Hold from Clock Maing     | LXHQX              | SM2 = 1:4 clocks per cycle                           | t <sub>CLCL</sub>    | 113   |

| Input Data Hold After Clock Rising    | 4                  | SM2 = 0:12 clocks per cycle                          | t <sub>CLCL</sub>    | no    |

| Input Data Hold After Clock Rising    | $t_{XHDX}$         | SM2 = 1:4 clocks per cycle                           | 0                    | ns    |

| Clock Rising Edge to Input Data Valid | t <sub>xhov</sub>  | $_{\star}$ SM2 = 0:12 clocks per cycle 11 $t_{CLCL}$ |                      | ns    |

| Clock Mising Luge to Input Data Valid | •XHDV              | SM2 = 1:4 clocks per cycle                           | 2 t <sub>clcl</sub>  | 115   |

Figure 26. Serial Port 0 (Synchronous Mode)

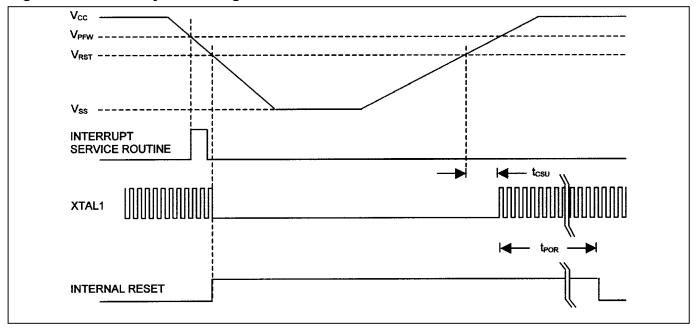

### **POWER-CYCLE TIMING CHARACTERISTICS**

| PARAMETER                      | SYMBOL           | TYP | MAX    | UNITS             |

|--------------------------------|------------------|-----|--------|-------------------|

| Crystal Startup Time (Note 14) | t <sub>csu</sub> | 1.8 |        | ms                |

| Power-On Reset Delay (Note 15) | t <sub>POR</sub> |     | 65,536 | t <sub>clcL</sub> |

**Note 14:** Startup time for crystals varies with load capacitance and manufacturer. Time shown is for an 11.0592MHz crystal manufactured by Fox Electronics.

Figure 27. Power-Cycle Timing

Note 15: Reset delay is a synchronous counter of crystal oscillations during crystal startup. Counting begins when the level on the XTAL1 input meets the V<sub>IH2</sub> criteria. At 40MHz, this time is approximately 1.64ms.

### **PIN DESCRIPTION**

| PIN              |                                           | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|------------------|-------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LQFP             | PLCC                                      | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 8, 22, 40,<br>56 | 17, 32, 51,<br>68                         | V <sub>cc</sub> | +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 9, 25, 41,<br>57 | 1, 18, 35,<br>52                          | GND             | Digital Circuit Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 46               | 57                                        | ALE             | Address Latch Enable, Output. When the $\overline{\text{MUX}}$ pin is low, this pin outputs a clock to latch the external address LSB from the multiplexed address/data bus on Port 0. This signal is commonly connected to the latch enable of an external transparent latch. ALE has a pulse width of 1.5 XTAL1 cycles and a period of four XTAL1 cycles. When the $\overline{\text{MUX}}$ pin is high, the pin will toggle continuously if the ALEOFF bit is cleared. ALE is forced high when the device is in a reset condition or if the ALEOFF bit is set while the $\overline{\text{MUX}}$ pin is high. |  |  |  |

| 45               | 56                                        | PSEN            | Program Store Enable, Output. This signal is the chip enable for external ROM memory. PSEN provides an active-low pulse and is driven high when external ROM is not being accessed.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 47               | 58                                        | ĒĀ              | <b>External Access Enable, Input.</b> This pin must be wired to GND for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 26               | 36                                        | MUX             | <b>Multiplex/Demultiplex Select, Input.</b> This pin selects if the address/data bus operates in multiplexed $(\overline{MUX} = 0)$ or demultiplexed $(\overline{MUX} = 1)$ mode.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 2                | 11                                        | RST             | Reset, Input. The RST input pin contains a Schmitt voltage input to recognize external active-high reset inputs. The pin also employs an internal pulldown resistor to allow for a combination of wired-OR external reset sources. An RC circuit is not required for power-up, as the device provides this function internally.                                                                                                                                                                                                                                                                                |  |  |  |

| 3                | 12                                        | RSTOL           | Reset Output Low, Output. This active-low signal is asserted: When the processor has entered reset through the RST pin, During crystal warmup period following power-on or stop mode, During a watchdog timer reset (2 cycles duration), During an oscillator failure (if OFDE = 1), Whenever $V_{CC} \leq V_{RST}$ .                                                                                                                                                                                                                                                                                          |  |  |  |

| 23               | 33                                        | XTAL2           | XTAL1, XTAL2. Crystal oscillator pins support fundamental mode, parallel resonant, and AT-cut crystals. XTAL1 is the input if an                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 24               | 34                                        | XTAL1           | external clock source is used in place of a crystal. XTAL2 is the output of the crystal amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 55               | 67                                        | AD0/D0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 54               | 66                                        | AD1/D1          | <b>AD0–7 (Port 0), I/O.</b> When the $\overline{\text{MUX}}$ pin is wired low, Port 0 is the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 53               | 65                                        | AD2/D2          | multiplexed address/data bus. While ALE is high, the LSB of a memory address is presented. While ALE falls, the port transitions to                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 52               | 52 64 AD3/I<br>51 63 AD4/I<br>50 62 AD5/I |                 | a bidirectional data bus. When the $\overline{MUX}$ pin is wired high, Port 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                  |                                           |                 | functions as the bidirectional data bus. Port 0 cannot be modified by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                  |                                           |                 | software. The reset condition of Port 0 pins is high. No pullup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 49               | 61                                        | AD6/D6          | resistors are needed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 48               | 59                                        | AD7/D7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

### **PIN DESCRIPTION (continued)**

| P                                        | IN                                           | NAME                     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------------------------|----------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP                                     | PLCC                                         | NAME                     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 58–64, 1                                 | 2–8, 10                                      | P1.0–P1.7                | <b>Port 1, I/O.</b> Port 1 can function as an 8-bit bidirectional I/O port, the nonmultiplexed A0–A7 signals (when the $\overline{\text{MUX}}$ pin = 1), and as an alternate interface for internal resources. Setting the SP1EC bit relocates RXD1 and TXD1 to Port 5. The reset condition of Port 1 is all bits at logic 1 through a weak pullup. The logic 1 state also serves as an input mode, since external circuits writing to the port can overdrive the weak pullup. When software clears any port pin to 0, a strong pulldown is activated that remains on until either a 1 is written to the port pin or a reset occurs. Writing a 1 after the port has been at 0 activates a strong transition driver, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again becomes the output (and input) high state. |  |  |  |  |

|                                          |                                              |                          | Port Alternate Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 58                                       | 2                                            | A0                       | P1.0 T2 External I/O for Timer/Counter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 59                                       | 3                                            | A1                       | P1.1 T2EX Timer/Counter 2 Capture/Reload Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 60                                       | 4                                            | A2                       | P1.2 RXD1 Serial Port 1 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 61                                       | 5                                            | A3                       | P1.3 TXD1 Serial Port 1 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 62                                       | 6                                            | A4                       | P1.4 INT2 External Interrupt 2 (Positive Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 63                                       | 7                                            | A5                       | P1.5 INT3 External Interrupt 3 (Negative Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 64                                       | 8                                            | A6                       | P1.6 INT4 External Interrupt 4 (Positive Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 1                                        | 10                                           | A7                       | P1.7 INT5 External Interrupt 5 (Negative Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 35                                       | 46                                           | A8 (P2.0)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 36                                       | 47                                           | A9 (P2.1)                | A15–A8 (Port 2), Output. Port 2 serves as the MSB for external addressing. The port automatically asserts the address MSB during                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 37<br>38                                 | 48<br>49                                     | A10 (P2.2)<br>A11 (P2.3) | external ROM and RAM access. Although the Port 2 SFR exists, the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 39                                       | 50                                           | A11 (P2.3)<br>A12 (P2.4) | SFR value never appears on the pins (due to memory access).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 42                                       | 53                                           | A13 (P2.5)               | Therefore, accessing the Port 2 SFR is only useful for MOVX A, @Ri or MOVX @Ri, A instructions, which use the Port 2 SFR as the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |